红军长征的原因 为什么长征后就安全了

在阅读此文前,诚邀您点击一下“关注”,既方便您进行讨论与分享,又给您带来不一样的参与感,感谢您的支持。

1934年,蒋介石在围剿红军屡次受挫后,终于狠下心来制定十分劳民伤财的“铁桶计划”,意图一举歼灭红军。

该计划的规模前所未有之大,一旦计划顺利执行,红军将全军覆没。

可蒋介石万万没想到,作战会议刚开完,这份机密军要就由红军情报人员假扮乞丐秘密送往瑞金,让计划彻底泡汤。

这位红军情报员是谁?他是如何获得情报的?

1934年9月下旬,蒋介石召集200多名国民党高官,在江西庐山召开军事会议。

蒋介石亲自主持会议,他参考并汇总在场各高官的想法,集众人之所长形成了一个考虑严密的计划,名为“铁桶”计划。

蒋介石严密估算红军人数,认为现存红军不过10万人。为了确保能够歼灭红军,他首先决定启动人数优势,以15比1的比例开展人海战术,调集150万军队待命。

此外,蒋介石下令调集200门大炮、270架飞机协同作战,保证己方火力优势。

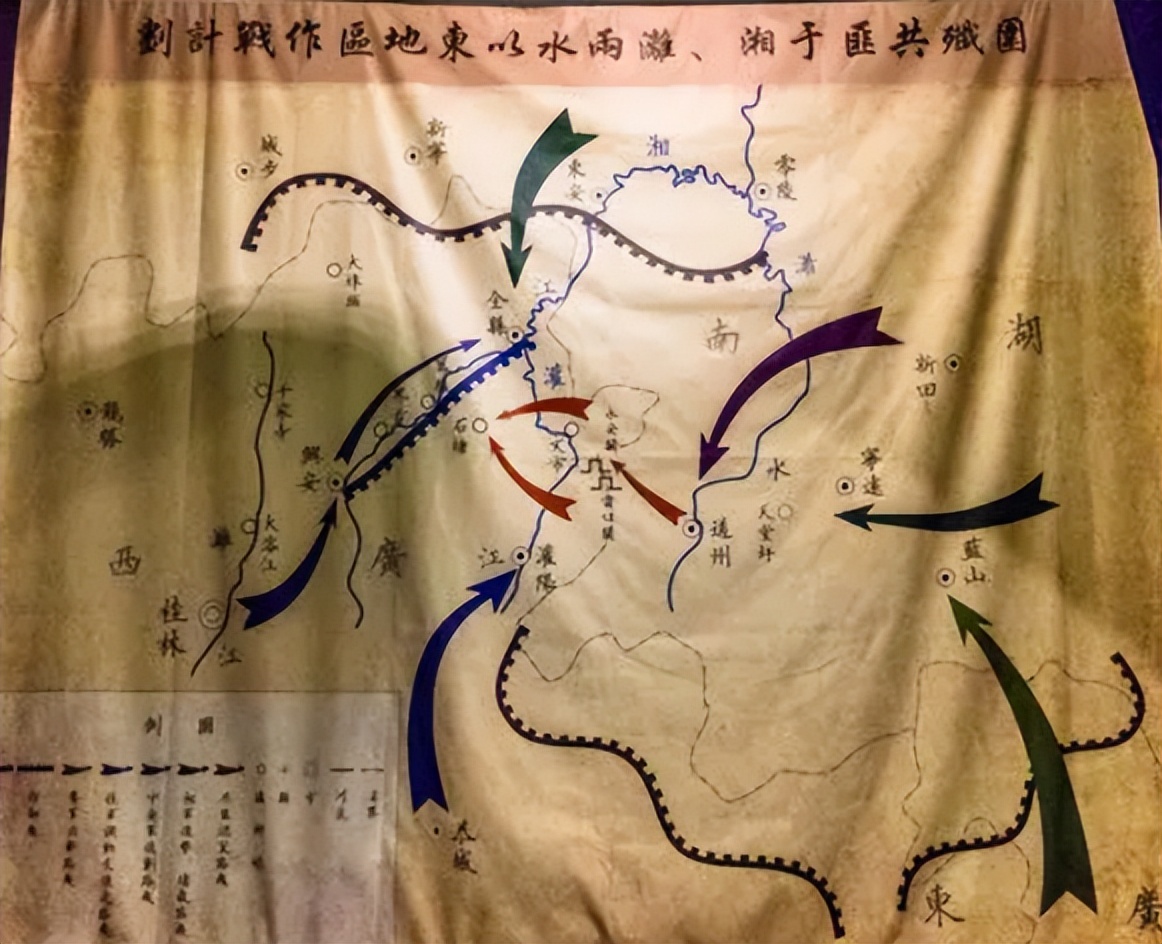

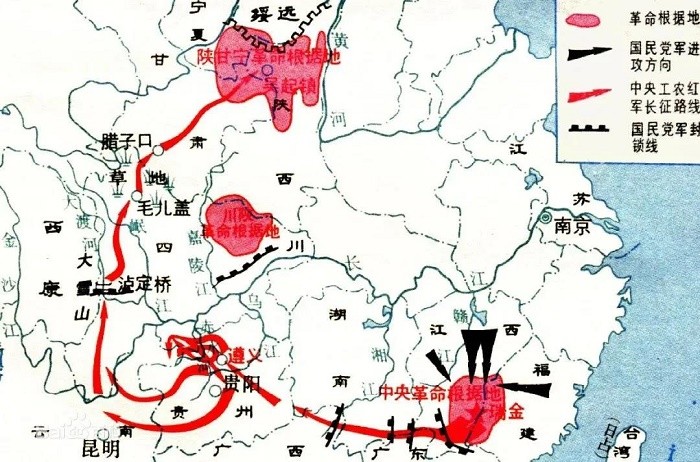

此计划之所以称之为“铁桶”,是因为蒋介石要求将领们从各镇守地出发,严格按照计划,在同一时间分别攻打不同地域,力求以瑞金为中心形成严密的包围圈。

按照计划,国民党军队将在包围圈形成后,于内部逐步建起30道铁丝网和严密的火力封锁线,缩小红军活动范围,逼迫红军在极小范围内进行决战。

为确保这个大型计划得以顺利实施,在庐山举行的这场会议持续6天,各将领高官不断进行讨论完善计划,与会人员在会议结束后都得到一本重达几斤的阐述文件。

蒋介石对此计划信心满满,国民党将领们更是各个摩拳擦掌要拿红军开刀。

此时,中央红军在博古和李德的领导下正深陷“左倾”错误,固守红军领地,若蒋介石的计划顺利施行,那么红军无疑会全军覆没。

但蒋介石没想到,这份计划仅在会议结束一晚后,就变成写满密码的字典被送往瑞金,成为9万红军长征的契机。

促成此事的两位关键人物,就是莫雄和项与年。

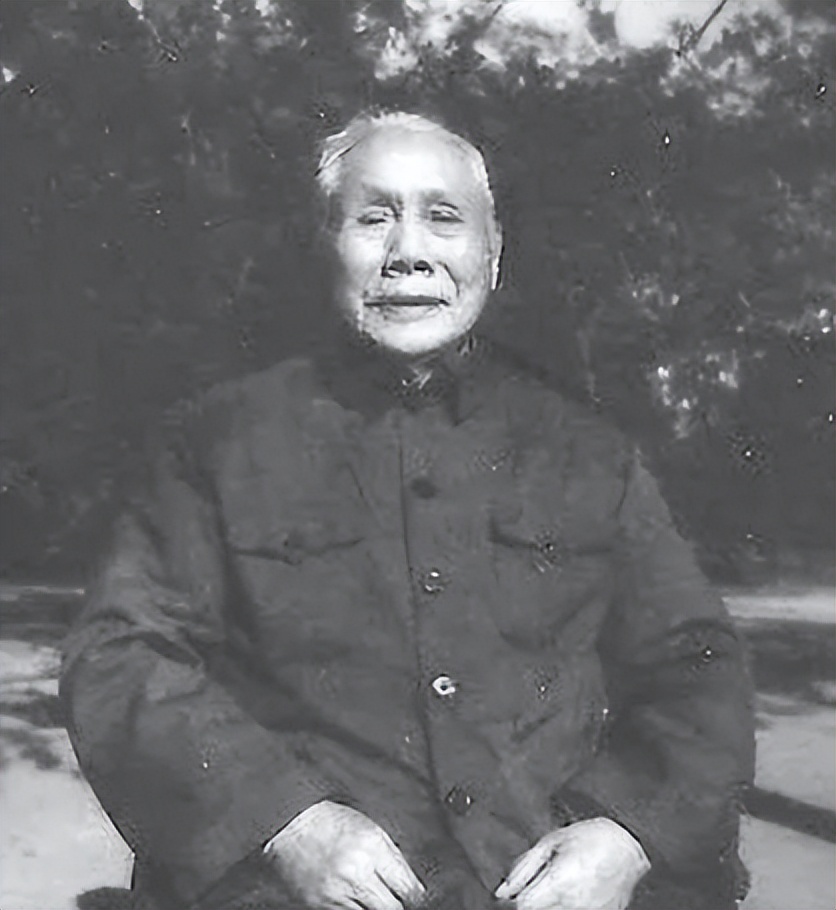

“铁桶计划”是名副其实的绝密,如果流出,必然是与会人员中有人泄密。这个人,就是莫雄将军。

1934年,莫雄虽然已经是将军,但其军功和军衔并不足以进入庐山这场军事会议。蒋介石破格喊他参加会议的原因有二:一是莫雄曾救过蒋介石,二是莫雄为“剿共”做出不斐贡献。

1922年,蒋介石前往桂林讨伐吴佩孚,时任大本营参军兼粤军第二军总参谋长。一次,他留守大本营,却意外被桂林当地的近十万人“土匪”包围,情况十分危机。

惊慌失措下,蒋介石发电报向当地驻军求援。而解了蒋介石燃眉之急的人,就是粤军第四独立旅旅长莫雄。莫雄带领两个营冒死营救,这才让蒋介石脱离生命危险。

经过此事,蒋介石对莫雄始终抱有感激之情。即使1927-1930年莫雄协助张发奎搞反蒋活动,蒋介石也没有对莫雄痛下死手,只是在1930年剥夺莫雄军权让他前往上海,赋闲在家。

莫雄就是在上海接触到曾经的部下,此时的中共党员刘亚佛。

要知道,莫雄是坚定的孙中山思想拥护者,也正是因为他对革命的执著才进行了反蒋活动。莫雄在和刘亚佛交流过后,对中共拥护的马克思主义思想产生了共鸣。

在刘亚佛的引荐下,莫雄和许多共产党员(包括周恩来)产生交集。每当莫雄对革命事业感到迷茫时,周恩来总以马克思主义思想开导他。很快,莫雄十分诚心地提出入党申请。

莫雄的思想觉悟、功绩本领完全符合入党条件。但考虑到莫雄在国民党的地位,以及他在国民党能够做出更多贡献,党中央拒绝他的入党申请,并希望莫雄利用他的身份帮助我党。

莫雄同意党中央的这个安排,在此后的日子中为我党做出巨大贡献。

时间到了1933年,蒋介石在几次剿共的过程中频频受挫,十分挫败。10月,蒋介石的高级幕僚杨永泰在南昌遇到了莫雄,一番交谈后他起了重用莫雄的心思。

在心腹杨永泰的介绍下,蒋介石想起用兵神人莫雄,于是他决定将莫雄任命为江西德安区专员兼保安“剿共”司令,并放权让莫雄自己组成军事班子。

莫雄借此机会,将项与年、刘亚佛、卢志英三名中共党员纳入他的“剿共”领导班子。还给杨永泰推荐许多中共党员,让很多人打入国民党内部。

莫雄在出任赣北第四行政专署专员和保安司令后,同中央红军上下通气,演了一场大戏。

莫雄负责的分区内,红军队伍故意和莫雄领导的队伍几次交火,然后佯装不敌仓皇撤退。莫雄接连打胜仗的消息传到蒋介石耳中,让他十分高兴,对莫雄的信任也更多几分。

这才有了破格让莫雄参与庐山军事会议,拿到机密军要文件一事。

会议上,莫雄看似兴奋万分摩拳擦掌要打共匪,内心已经万分焦灼恨不得长翅膀飞往瑞金通风报信。六天会议结束,莫雄揣着这份文件赶忙跑下山找到了项与年、刘亚佛、卢志英三人。

项与年三人看莫雄神态不对,拿过文件快速阅读。看完文件后,三人皆出了一身冷汗。他们都看出这次红军队伍面临的凶险。

三人虽很想将文件送往瑞金,考虑到莫雄的性命安全又十分踌躇。莫雄看穿三人顾虑,当即要求三人不要顾虑他,赶紧将文件送往党中央所在地,以最大程度上保全红军队伍有生力量。

看到莫雄如此深明大义,为革命事业奋不顾身的表现,三人对莫雄表现出极大感激。

时间紧急,项与年、刘亚佛和卢志英彻夜不眠,将文件翻译成密文记载到四本学生字典上。

三人首先将文件的核心内容发往南昌联络部,要求联络部发往瑞金告知中央红军领导,而后由项与年将整套资料秘密送往瑞金。

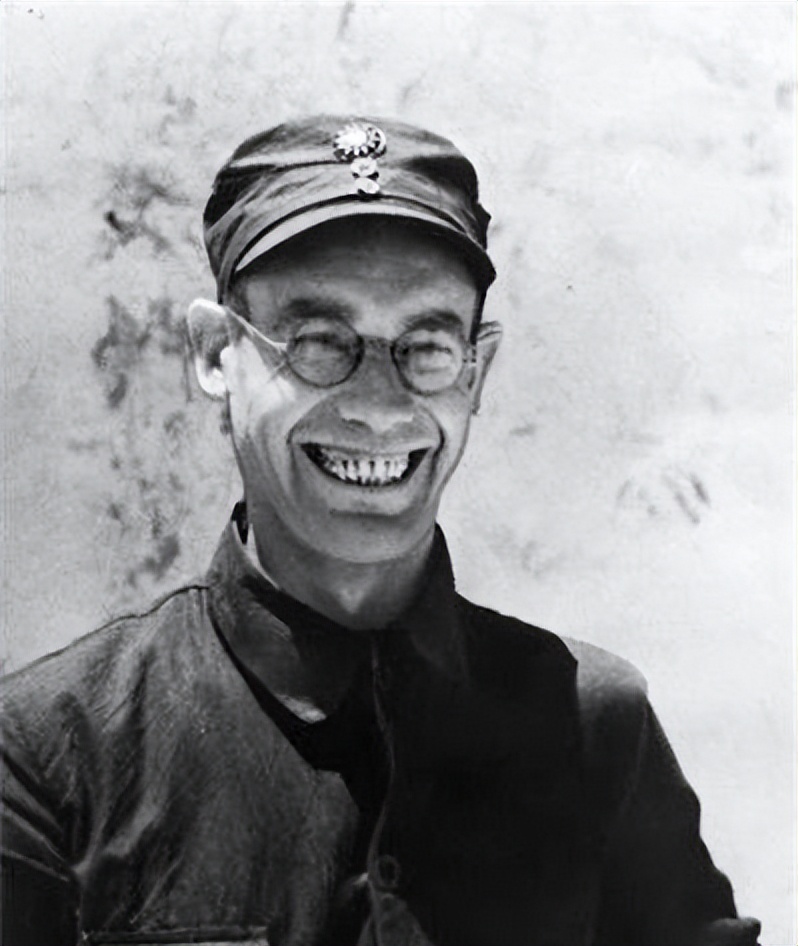

让项与年送文件主要有以下考虑:第一,项与年外貌上最为儒雅,扮作教师可以降低国民党士兵的警惕性;第二,他长期从事地下党工作,遇过最多情况,应变力相当强。

最为重要的一点,就是项与年是三人中对瑞金附近的地形最为熟悉的人。此外,项与年还会说客家话,在巡查士兵面前的伪装能更到位。

刘亚佛、卢志英和项与年对南昌到瑞金的沿路敌情进行分析,决定让项与年从南昌乘车前往吉安,后徒步进入泰和山区,途径兴国、于都,最终到达瑞金的路线。

项与年马不停蹄地踏上了运送资料的旅程。

从南昌出发时,项与年还能凭借教书先生的身份顺利过关,但进入泰和山区后,国民党士兵对过往人员的排查变得更加仔细。

项与年认为写满密文的字典很容易被搜查,于是他将字典内的密文抄在纸张上,将纸垫在鞋里继续前行。

走了没多远,项与年长期搞地下工作的直觉告诉他,垫在鞋里也有被搜查的可能性,必须选择更保险的做法。

重重困境下,项与年决定尽量避开岗哨,在夜里赶路。泰和山区山路崎岖,摸黑前行让项与年吃了很大苦头,很快就摔得浑身是伤。

可这也只是项与年在这段路程中遇到的最小困难。昼伏夜出的生活让项与年没机会补充水和粮食,渴了找溪水,饿了吃野果成为那几天的常事。

不过几天,项与年浑身沾满灰尘,饿的瘦骨嶙峋。即使如此,项与年凭着坚强的意志力,依旧不断向前。

等项与年跋山涉水到了兴国,他发现事态已经十分严重,“铁桶”计划在这里已经初初成型,各个村子都有岗哨,隔不了多远就有国民党士兵修筑的碉堡。

士兵们对外人的检查十分严苛,面生的青壮年一旦接近,就会被当做“赤匪侦探”抓起来。

比兴国严苛的检查状况更让项与年焦虑的是,他在此处耽搁的时间越长,红军生存的概率就越低。

想想瑞金一无所知的广大战友们,项与年心一横,用伤害自己的方式为将近9万红军赢得生机。

他躲回山林里,趁着月色,捡起一块石头对着自己的门牙就砸下去。一颗门牙掉下,项与年已是满嘴鲜血,痛得发抖;但他没有停下动作,接连将自己剩余的三颗上下门牙全部敲掉。

此时,项与年长途跋涉中已经满是脏污的衣服上沾满了他自己的鲜血。而失去牙齿的痛更是让他神情恍惚。

等到天色泛白,蓬头垢面双颊涨得通红的项与年,带着满身的酸臭气朝岗哨摇摇晃晃地走去,根本看不出他从南昌出发时儒雅的扮相。

项与年这一副被世道折磨得遍体鳞伤的乞丐扮相很好地迷惑了检查的士兵,士兵一脸嫌恶摆摆手放他过了关卡。

10月7日,项与年凭着意志力深一脚浅一脚走到瑞金中央红军的驻地,看到驻守阵地的红军同僚时,他已经累得快说不出话。

项与年一屁股坐在地上,朝同僚摆手,虚弱地说他要见周恩来。他的情况很快被层层上报,顺利见到了周恩来。

周恩来看着眼前如此狼狈的项与年不由大吃一惊,但项与年并没有给周恩来细想的时间。他强撑精神把写满密文的资料拿给周恩来,并向周恩来汇报情况。

周恩来听完汇报深感情况危急,命令红军作战情报部门将密文翻译成文件,交给博古与李德看,同时联系党中央,将瑞金情况逐一汇报。

危机情况下,党中央迅速反应提出红军要实行大规模战略转移。

10月8日,红军地方部队接替各战线防御工作,红军主力部对则集体向于都集合。

红军只留下少数队伍吸引蒋介石部队火力,确保蒋介石不会起疑,其余共计86489名红军战士全部参与了这次震惊世界的长征之旅。

半个月后,蒋介石的“铁桶”计划终于实行到最后阶段,就剩占领瑞金,却在这时发现瑞金已经是一座空城,哪里还有红军部队的影子。

莫雄与项与年此次冒险送情报的举动,有两个功劳:

一方面,这次行动粉碎蒋介石“剿共”阴谋,让红军主力得以保全;

另一方面,情报中关于国民党实力的客观分析,让博古认清国共实力差距,打消了博古和李德的“左倾”主义冒进思想,有利于遵义会议上对战略错误的纠正。

蒋介石精心设计的计划一朝破产,勃然大怒。他下令彻查国民党内部将领却没有发现任何泄密痕迹,莫雄得以保全。

此后的日子里,莫雄潜伏在国民党,利用身份在救援我党伤员、抗日战场。解放战场等多方面发光发热。虽然在工作过程中几次受到蒋介石猜疑,但仍旧平安无事活到建国后。

至于项与年,他本该在送完情报后跟随大部队进行长征,但中央特科又一次将艰巨的使命交予他。

为了防止蒋介石不死心对我方红军穷追猛打,中央特科认为有必要派人干扰敌方位于南昌的后勤运输线。从经验到性格挑选一圈,特科认为这个任务只能由项与年带人完成。

让人想不到的是,项与年一到南京就意外被国民党士兵抓住了。

还好项与年身上一直装着身为莫雄部下时的身份证明,让国民党士兵没有对他痛下杀手,只是决定将他押回南昌。

去往南昌的途中,项与年趁敌人不备逃了出来,在外辗转一个月回到上海。特科考虑到外头正在追捕项与年,特批他和家人团聚一个月。一个月后,项与年继续为了革命事业奋斗。

只是在项与年离开家后不久,他的住所位置就暴露了,他的妻子和女儿遭受严刑拷打相继离世,只有儿子因上学没有在家逃过一劫。

项与年此后为了革命事业改名为梁明德,也在抗日战场和解放战争中发挥重要作用。

到了今天,人人知道红军长征,却无人听闻莫雄与项与年。这是无数个莫雄与项与年用他们的付出堆砌出的美好未来。

我们享受着前人付出得来的成果,也该铭记莫雄与项与年为创造美好生活做出的贡献。

杨晓璐.党外奇人莫雄二三事[J].党史纵览,2019(02):42-45.

王俊彦.送绝密情报的奇人奇功——莫雄与项与年[J].百年潮,2013(07):29-35

周军.解密十万红军脱险的绝密情报[J].党史纵览,2016(10):27-31.

交警电话是多少 24小时道路救援电话

前来说,交通违法申诉只能本人亲自到车管所申请一种方法,网络、电话都无法进行违章申诉。按照相关规定:被处罚人不服公安交通管理机关的警告、罚款和拘留等裁决的,可以在领取处罚决定书之日起的十五天内到主管公安机关或者上一级公安交通管理机关提出申诉。大财经2023-03-20 19:28:140000参公事业单位 省考参公编制好不好

甘肃省甘南生态环境监测中心为甘肃省生态环境厅直属参公管理事业单位,主要从事甘南州辖区内水、气、声、土的监测分析工作。因工作需要,在核定编制外,公开招聘1名环境监测人员。一、招聘原则坚持“公开、公平、公正、择优”原则,按照德才兼备的用人标准,采取公开报名、资格审核、面试、考察、体检、聘用等程序公开招聘,接受有关部门和社会监督。二、招聘条件(一)具有中华人民共和国国籍;0002五指毛桃和什么煲汤最好 五指毛桃的最佳搭配

大财经2023-03-21 06:18:040001营业执照怎么年审 个体营业执照年报入口

营业执照是工商行政管理机关发给工商企业、个体经营者的准许从事某项生产经营活动的凭证。创立公司首先需要做的就是办理营业执照,有些人办理完营业执照就不管不问了,并不是办理好营业执照就万事大吉,还需要在一定的时间进行年检,那么工商营业执照年检(营业执照年检怎么办理网上怎么操作),下面由企的宝财税给大家详细介绍下。http://www.gsxt.gov.cn/国家企业信用信息公示系统大财经2023-03-20 18:27:170000把一件事做到极致,远胜于把一万件事做得平庸

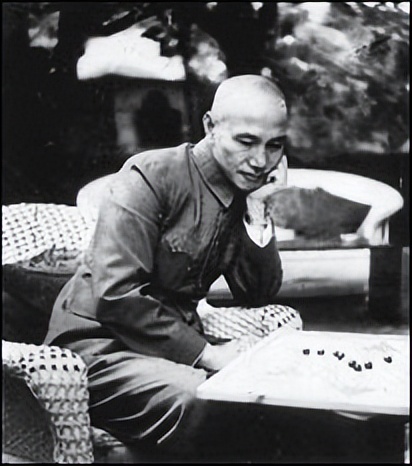

与其花许多时间和精力去凿许多浅井,不如花同样的时间和精力去凿一口深井。——罗曼·罗兰有一次比尔·盖茨和巴菲特聚会,盖茨的爸爸让两位巨富,只用一个词总结自己的成功。他俩不约而同地写下了一个词——Focus(专注)。专注做一件事,把这件事做到极致,远胜于把一万件事做得平庸。专注博二兔,不得一兔。——吴清源今年97岁的“寿司之神”小野二郎,是全世界年纪最大的三星主厨。大财经2023-07-27 00:29:140000